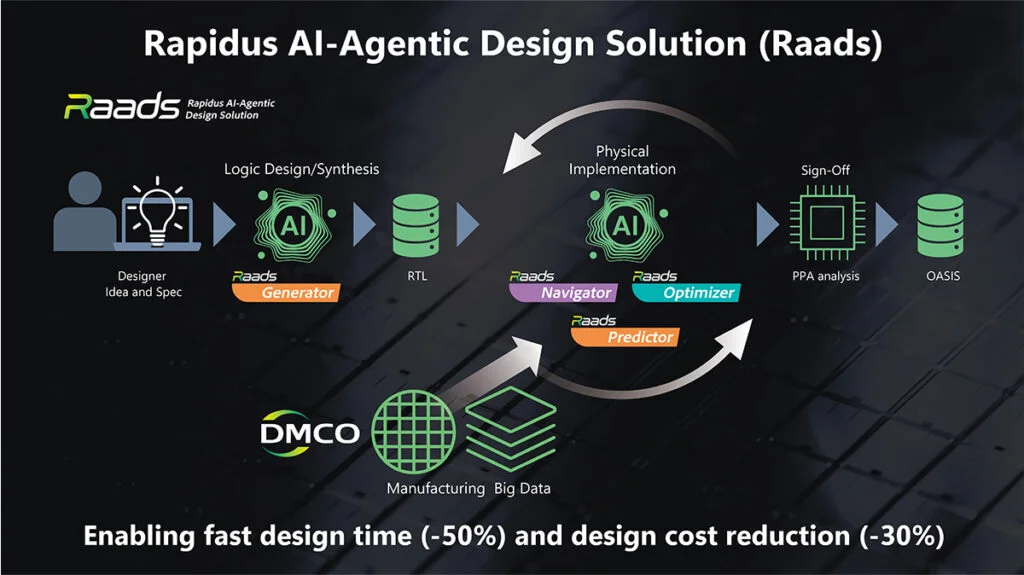

2025 年 12 月 17 日,Rapidus Inc. 宣布推出一组体现该公司“Raads”概念的工具,以推广 RUMS(快速统一制造服务)。将从 2026 年起依次发布。Raads 由多个工具组成,并与 PDK(工艺设计套件)和参考流程一起提供给客户。之前设想的“Rapidus AI 辅助设计解决方案”将演变成“Rapidus AI 代理设计解决方案”。通过将 Raads 与现有 EDA 工具结合使用,可以将设计时间缩短 50%,设计成本降低 30%。

提供的主要工具是“Raads Generator”(一种基于LLM的EDA工具)和“Raads Predictor”(一种RTL调试和物理设计/布局和布线优化工具)。未来,“Raads Navigator”、“Raads Indicator”、“Raads Manager”、“Raads Optimizer”将陆续发布。到2025年6月,该公司的IIM-1将连接200多台全球最先进的单晶圆半导体制造设备,开始2nm GAA晶体管的原型生产,并确认运行。

从: ![]() Rapidus利用AI体现了独特的“Raads”概念〜设计支持工具的顺序发布〜

Rapidus利用AI体现了独特的“Raads”概念〜设计支持工具的顺序发布〜

【编辑部评论】

Rapidus在日本半导体产业复兴的历史背景下宣布的AI设计工具“建议”其战略意义超越单纯的技术创新。

半导体设计的最大瓶颈是设计周期延长和成本上升。尖端的 2nm 工艺给仅使用传统 EDA(电子设计自动化)工具的设计人员带来了巨大的负担。 Rapidus 这次宣布的 Raads 就是针对这一挑战的答案。我们提供一整套利用 LLM(大规模语言模型)和机器学习的设计支持工具。

值得注意的是,从“AI辅助”到“AI代理”的概念转变。这意味着人工智能不仅仅是一个辅助工具,而是一个积极参与设计过程的“代理”。当设计人员输入规格时,Raads Generator 自动生成针对 Rapidus 2nm 工艺优化的 RTL(寄存器传输级别)设计数据,Raads Predictor 快速预测 PPA(功耗、性能、面积)。

通过这个系统,我们设定了具体的数字目标,即减少 50% 的设计时间和 30% 的设计成本。这对半导体行业影响巨大。在与台积电和三星等现有大型代工厂的竞争中,Rapidus 在技术节点上落后了一步,但它希望通过显着缩短设计到制造周期时间来实现差异化。

Rapidus的优势在于IIM-1工厂采用的全步骤单晶圆工艺。与传统的批量处理不同,一次处理一个晶圆可以收集更详细的数据,然后用于训练人工智能模型。到 2025 年 6 月,他们连接了 200 多个最先进的设备,并于 7 月开始制作 2nm GAA 晶体管原型并成功确认其运行,这一事实显示出令人难以置信的速度感。

另一方面,也存在挑战。 Rapidus的目标是在2027年开始量产,届时台积电可能已经转移到下一代节点。此外,在获取客户方面,与拥有良好业绩记录的现有代工厂竞争并不容易。然而,开发自己的 AI 设计工具(如 Raads)并将其与 PDK(工艺设计套件)作为一套提供,以降低设计门槛并赢得更多客户是有意义的。

日本政府已决定提供约1.72万亿日元支持,表明该国有意将振兴半导体产业上升为国家战略。还有报道称,作为与IBM技术合作的一部分,该公司的工程师正被派往北海道的一家工厂,这表明技术转让正在稳步推进。

Raads 的真正价值可能在于半导体设计的民主化。它有潜力扩大创新范围,使中小型企业和初创公司能够使用尖端流程进行设计,而这些流程以前只有少数大公司通过人工智能支持才能使用。

【术语解释】

RTL(寄存器传输级别)

半导体设计中的一种抽象级别,将数字电路的操作描述为寄存器之间的数据传输。它是用Verilog或VHDL等硬件描述语言编写的,并使用逻辑综合工具转换为门级电路。设计人员可以在高层定义电路功能,而无需担心物理实现细节。

EDA(Electronic Design Automation / 电子设计自动化)

支持半导体芯片设计、验证和制造准备的软件工具的总称。它自动化芯片设计的每个过程,包括电路图创建、逻辑综合、布局和布线以及时序验证。 Synopsys、Cadence 和西门子 EDA 是行业领导者。对于涉及数十亿晶体管的现代复杂半导体设计至关重要。

PDK(工艺设计套件)

特定制造过程的设计数据包。包含器件模型、设计规则、标准单元库等。设计人员可以利用它来设计可制造的电路。铸造厂提供的连接设计和制造的重要工具。

PPA(功率性能区)

半导体设计中的三个重要评估指标。 Power(功耗)、Performance(性能/运行速度)和Area(芯片面积)的缩写。这些是一种权衡关系,设计者需要根据应用找到最佳平衡点。 AI 设计工具可自动执行 PPA 优化。

GAA(周围栅极)晶体管

下一代晶体管结构之一,其中栅极围绕沟道的整个圆周。它比传统FinFET具有更好的栅极可控性,并且可以进一步小型化。台积电和三星也将其作为继2nm工艺之后的主要技术。

LLM(大语言模型)

在大量文本数据上训练的大规模神经网络模型。它可以理解并生成自然语言,并用于 ChatGPT 等应用程序。 Rapidus 使用 LLM 从半导体设计规范的输入生成 RTL 代码。

单晶圆加工

一种逐片加工晶圆的制造方法。与传统的批量处理不同,可以从每个晶圆收集详细数据。 Rapidus 已将其引入到所有流程中,并利用 AI 对其进行流程优化。

RUMS(快速统一制造服务)

Rapidus提出的一种新的代工服务模式。它集成了设计、晶圆制造和 3D 封装,以缩短周期时间。一种结合了单晶圆处理和人工智能设计工具的独特方法。

2纳米工艺

半导体制造领域的尖端工艺技术。晶体管的栅极宽度标称为2纳米(与实际物理尺寸不同)。据称比7nm芯片性能提升45%,功耗降低75%。台积电的目标是2025年开始量产,Rapidus的目标是2027年。

[参考链接]

瑞必达有限公司(外部)

2022年成立的日本半导体代工公司。2nm兼容工厂IIM-1正在北海道千岁市建设。

IBM 研究部 – 半导体(外部)

IBM 的半导体研究部门。开发2nm节点以下芯片、3D纳米片晶体管技术等。

新思科技(外部)

全球最大的EDA工具供应商。提供逻辑综合、验证、物理设计等综合工具。

节奏设计系统(外部)

EDA行业第二大公司。优势包括布局布线、模拟设计和验证工具。

TSMC(台湾积体电路制造公司)(外部)

全球最大的半导体代工厂。 2nm工艺将于2025年开始量产。

[参考文章]

Rapidus 推出用于先进半导体制造的新型人工智能设计工具(外部)

Rapidus 的官方英文新闻稿。 Raads 工具组的详细信息和数字目标已发布。

Rapidus 通过 2nm GAA 晶体管原型设计实现重要里程碑(外部)

2025 年 7 月里程碑公告。宣布完成器件连接并成功生产 2nm 原型机。

日本Rapidus将与台积电和三星争夺芯片霸主地位(外部)

分析Rapidus的战略定位。我们将讨论单晶圆工艺的优越性及其对日本半导体复兴的意义。

Rapidus展示2nm芯片原型,瞄准2027年量产(外部)

报道称计划将产能从每月 7,000 件增加到 25,000-30,000 件。

[编者后记]

如今,日本半导体产业再次站在世界前列的边缘,Rapidus面临的挑战是我们每个人面临的问题。 AI时代将需要什么样的半导体,设计和制造方法又该如何改变?

Raads 采用与台积电和三星不同的方法来显着缩短设计周期,这也为技术民主化带来了新的可能性。您对这个国家项目有何展望? innovaTopia编辑部将持续关注,直至2027年开始量产。